本研究團隊由李耀仁博士帶領,李老師曾在台灣半導體研究中心(TSRI)服務超過十六年,現仍兼任該中心研究員。團隊成員來自國內多所大學,研究工作主要在台灣半導體研究中心(TSRI)與陽明交通大學奈米中心進行。針對特殊或先進的製程模組,亦會與日本產業技術綜合研究所(AIST)及其他國際研究機構合作。

本實驗室的研究生能在完整的元件製作平台上接受訓練,並參與先進元件的開發與實作。畢業生皆具備紮實的半導體製程與元件整合能力,多數進入國內外主要科技公司服務。

前瞻級的研究平台:我們的研究工作主要在 TSRI 與陽明交大奈米中心兩大頂尖設施中執行,實驗室擁有ALD、小尺寸CMP、低功率電漿及完整量測環境,後續從低溫 (4k) 到高溫 (150°C) 的元件量測,都可以在本實驗室進行。親手操作業界等級的先進設備,實現最前瞻的研發構想。

高效的學習與傳承系統:不必從零開始摸索!在學長姊們努力下,我們已建立一套成熟的「先進元件製作平台」。這套系統化的流程能大幅縮短您的學習曲線,讓你能快速投入核心研究,專注於先進元件的開發與創新。

本實驗室聚焦於後摩爾定律時代的關鍵技術,並分為以下三個核心研究小組,探索未來電晶體元件的可能:

1.垂直電晶體整合小組 (VFET Integration Team)

專注於垂直通道電晶體(Vertical FET)的結構設計、製程開發與電性評估。

2.多晶矽/矽/鍺通道元件整合小組 (Ge FinFET/GAA/CFET Team)

以鍺基通道(Ge channel)為核心,研究 FinFET、GAA 與 CFET 等先進奈米元件之整合技術。

3.氧化物半導體元件整合組 (OS GAA/CFET Team)

聚焦於氧化物半導體(OS)材料的元件應用,探索其在 GAA 與 CFET 架構中的潛力與製程相容性

近期成果:

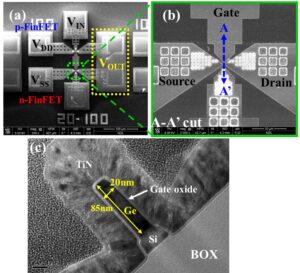

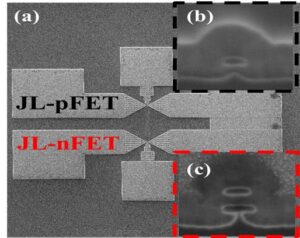

Fig1. Ge finFETs平台: 透過在SOI上磊晶Ge,我們所建立的Ge CMOS平台可以用來研究Ge在製作在元件上特性

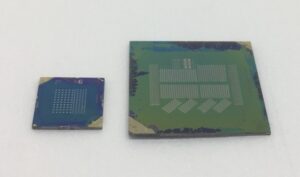

Fig2. 從八吋晶片到破片製程,我們不僅可以節省元件製作的成本,也讓吾人的’研究具有更大的彈性

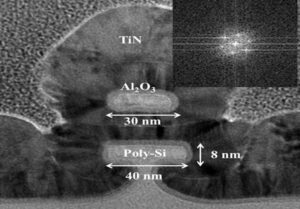

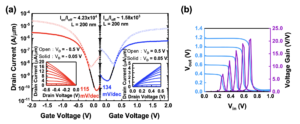

Fig3. 多晶矽的堆疊式元件平台

Fig4. 多晶矽的堆疊式元件平台可以透過微影與蝕刻,改變pFET與nFET的通道數量

- 不同的通道數量有助於促進電流的平衡

- 為何pFET的通道數量少一個?因為臨界電壓太偏向nFET

Fig5. 多晶矽CFET元件,IEDM 2019年發表

- pFET因為受到蝕刻的時間比較長,所以變得比較窄

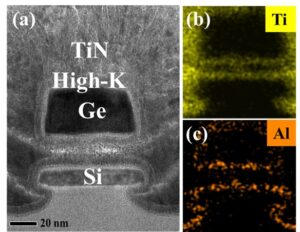

Fig6. 異質整合Ge/Si CFET元件

- 本實驗室與日本AIST合作,進行低溫bonding的製程,將Ge與Si鍵結一起,形成異質整合的CFET元件

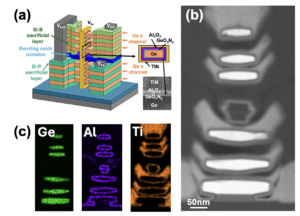

Fig7. 鍺基互補式場效應電晶體示意圖與電子顯微鏡影像/元素分佈。

- 本團隊目前已經透過磊晶與低溫Bonding的方式完成六層通道的Ge CFET (各三層的pFET/nFET)。該成果已經被IEEE EDL所接受。

Fig8. 鍺基互補式場效應電晶體輸出特性。

真空梭傳輸盒介紹-影片連結

- 在製程結束後,將sample直接進入真空盒,並進入分析儀器與設備對接,如此一來sample就不會接觸到大氣。